9月29日消息,据最新报道,amd正计划在未来的zen 6处理器中采用全新的d2d(die-to-die)互连技术,以替代沿用多年的serdes方案,而这一变革的初步迹象已在即将推出的strix halo apu上显现。

自Zen 2架构以来,AMD一直依赖SERDES PHY技术实现多个CCD(计算芯粒)之间的通信。然而,随着芯片集成度提升和性能需求增长,传统互连方式逐渐暴露出瓶颈。

SERDES即串行器/解串器,其作用是将各CCD产生的并行数据转换为串行信号进行跨芯片传输,接收端再通过解串器还原为并行数据。

这种方式存在两个显著问题:首先,串行化与解串行化过程需要额外功耗,用于时钟恢复、信号均衡及编码处理;其次,数据格式的转换不可避免地增加了芯粒间通信延迟,成为制约整体效率的关键因素之一。

随着NPU等新兴模块的引入,系统对低延迟、高效率带宽的需求愈发迫切。为此,AMD在Strix Halo APU的设计中进行了重大调整,这或许预示着Zen 6架构的发展方向。

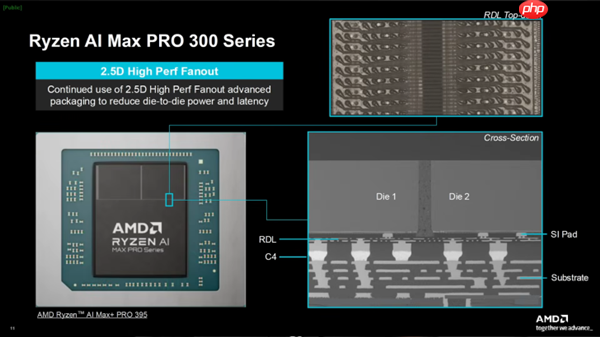

具体而言,AMD利用RDL(重分布层)在芯片之间布置了大量短距离、高密度的并行连接线路,这些线路嵌入于芯片下方的“中介层”结构中。

阶跃AI

阶跃AI

阶跃星辰旗下AI智能问答搜索助手

291 查看详情

291 查看详情

借助台积电的InFO-oS(集成扇出基板)封装技术,这些互连线被精确安置在硅芯片与有机基板之间,从而支持CPU核心通过宽幅并行接口直接通信。

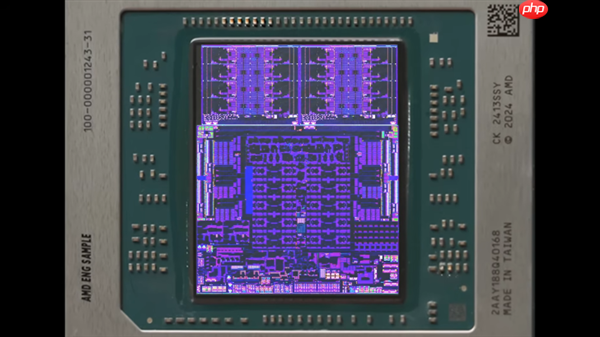

硬件分析团队High Yield在拆解研究Strix Halo时发现了这一变化:芯片表面出现了一个矩形的小型垫片区,正是InFO-oS技术的典型特征,而原本占据较大面积的大型“SERDES”模块已不见踪影。

这种新型D2D互连方案有效减少了功耗和通信延迟,因为它彻底省去了串行与并行之间的转换步骤。更重要的是,通过增加并行端口的数量,整体互联带宽实现了大幅提升。

但该方案也带来了新的设计挑战,尤其是在多层RDL布局方面,同时还需要重新规划布线优先级——由于芯片底部空间被用于扇出走线,可用资源变得更加紧张。

以上就是AMD下代Zen6 CPU大变革!转向全新D2D互连:能效延迟双飞跃的详细内容,更多请关注创想鸟其它相关文章!

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 chuangxiangniao@163.com 举报,一经查实,本站将立刻删除。

发布者:程序猿,转转请注明出处:https://www.chuangxiangniao.com/p/209922.html

微信扫一扫

微信扫一扫  支付宝扫一扫

支付宝扫一扫