9月2日,日本在半导体材料领域长期保持全球领先,然而由于缺乏完整的产业链支持,其在先进制程工艺上的进展一直未受关注。近年来,在日本政府的强力推动下,该国正逐步向高端芯片制造发起冲击。

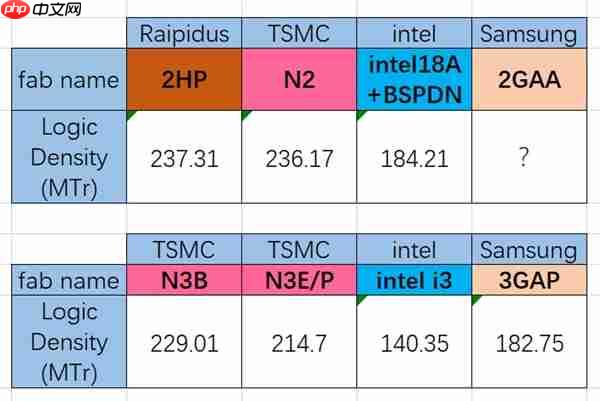

近日,日本新兴晶圆代工企业Rapidus公布了其2HP 2nm工艺的关键参数,其逻辑晶体管密度竟超越台积电N2工艺,且大幅领先于Intel 18A,引发业界震惊。

数据显示,Rapidus 2HP的逻辑晶体管密度达到每平方毫米2.3731亿个,略高于台积电N2的2.3617亿个,领先幅度不足5%,数值极为接近。

相比之下,Intel 18A尚未公布官方密度数据,行业普遍估算其约为每平方毫米1.8421亿个,这意味着Rapidus在该指标上领先近30%。

至于台积电的N3B/E/P、Intel 3以及三星3GAP等一众3nm级别工艺,均被远远甩在身后。

此外,Rapidus 2HP的单元库配置包含一个HD高密度库,单元高度为138Track,金属间距为G45。

不过,这一数据的真实性引发质疑。知名半导体分析机构TechInsights此前曾指出,台积电N2在高密度逻辑晶体管密度上实际达到了每平方毫米3.13亿个,Intel 18A也实现了约2.38亿个,甚至三星2GAA工艺也有约2.31亿个,这些数值均显著高于Rapidus所公布的指标。

百度作家平台

百度作家平台

百度小说旗下一站式AI创作与投稿平台。

146 查看详情

146 查看详情

需要强调的是,Intel 18A的晶体管密度低于台积电N2,并非技术落后,而是因其采用了创新的背面供电架构(BSPDN),占用了部分前道金属层空间,从而影响了密度表现。

更重要的是,Intel的设计重心并非单纯追求最高密度,而是更注重整体能效表现。

总体来看,若Rapidus公布的数据真实可信,至少表明日本在2nm工艺上已达到相当高的技术水平。但是否真正超越台积电与Intel,仍需进一步验证,尤其考虑到这是一家初创企业。

Rapidus计划于2026年第一季度发布2HP工艺的PDK(工艺设计包),并目标在2027年实现量产,但具体将用于哪些芯片产品目前尚无明确信息。

即便最终数据有出入,也不过是鞠个躬、道个歉的事罢了。

以上就是日本2nm密度竟然高于台积电N2!远超Intel 18A的详细内容,更多请关注创想鸟其它相关文章!

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 chuangxiangniao@163.com 举报,一经查实,本站将立刻删除。

发布者:程序猿,转转请注明出处:https://www.chuangxiangniao.com/p/252327.html

微信扫一扫

微信扫一扫  支付宝扫一扫

支付宝扫一扫