9月3日消息,%ignore_a_1%下一代zen 6架构的锐龙处理器将分别采用台积电2nm和3nm工艺来制造ccd与iod芯片。

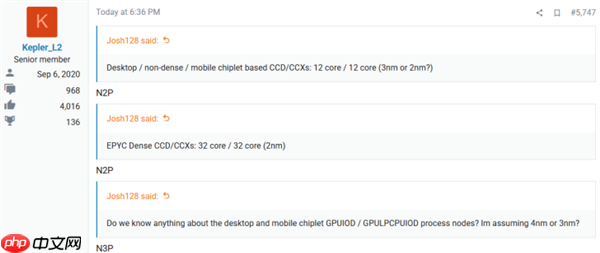

据爆料人Kepler_L2最新消息,AMD下一代锐龙CPU的计算芯片(CCD)将采用台积电N2P“2nm”工艺技术,而输入输出芯片(IOD)则会使用台积电N3P“3nm”工艺技术。

作为对比,当前Zen 5架构的锐龙处理器中,CCD采用的是4nm工艺,IOD则基于6nm工艺打造。

在Zen 6架构中,IOD芯片将整合内存控制器、USB、PCIe等I/O功能,并集成显示核心;而CCD则负责搭载Zen 6 CPU核心,每个CCD将拥有12个核心、24个线程以及48MB的L3缓存。

美间AI

美间AI

美间AI:让设计更简单

261 查看详情

261 查看详情

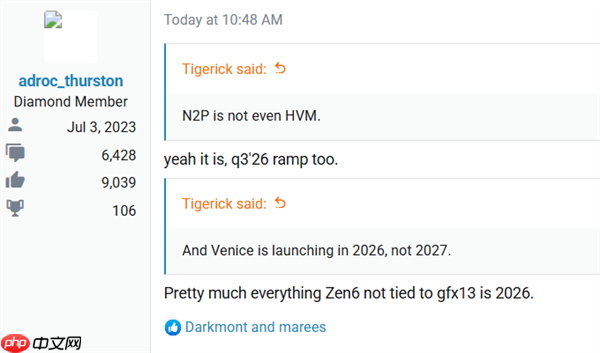

另有消息称,台积电的N2P工艺预计将于2026年第三季度进入量产阶段,因此基于Zen 6架构的全新锐龙处理器最早有望在2026年第三季度末或第四季度正式亮相。

值得一提的是,Intel的Nova Lake桌面处理器也计划在同一时期发布,但与Intel更换插槽不同,AMD将继续支持现有的AM5平台。

以上就是性能飞跃!AMD下代Zen6 CCD采用台积电2nm N2P:IOD为3nm N3P的详细内容,更多请关注创想鸟其它相关文章!

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 chuangxiangniao@163.com 举报,一经查实,本站将立刻删除。

发布者:程序猿,转转请注明出处:https://www.chuangxiangniao.com/p/880116.html

微信扫一扫

微信扫一扫  支付宝扫一扫

支付宝扫一扫