我们再从对可综合代码的支持角度来探讨systemverilog相较于verilog的优势。对于硬件设计,systemverilog引入了三种进程:always_ff、always_comb和always_latch。always_ff用于描述时序逻辑,对应fpga中的触发器,其内部应使用非阻塞赋值。

always @(posedge clk) 对应于 always_ff @(posedge clk)

always @* 对应于 always_comb 或 always_latch

SystemVerilog还引入了转换操作符,支持类型转换、位宽转换和符号转换。

类型转换:casting_type'(expression)

位宽转换:size'(expression)

符号转换:signed'(expression) 和 unsigned'(expression)

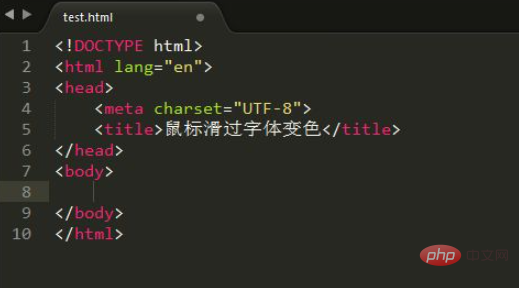

v1.5.2鲶鱼HTML编辑器HandyEditor

v1.5.2鲶鱼HTML编辑器HandyEditor

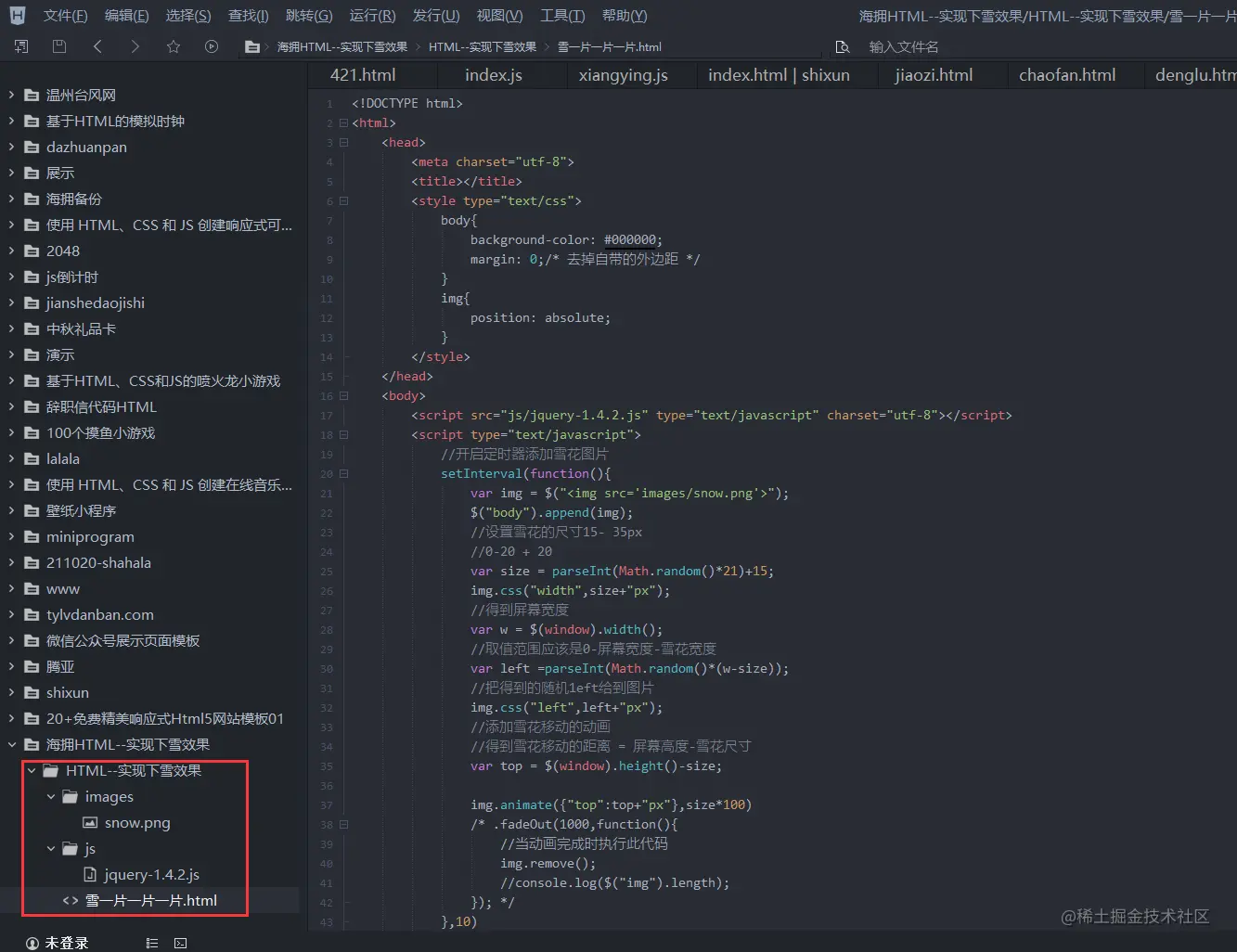

HandyEditor是由Catfish(鲶鱼) CMS出品的所见即所得富文本web编辑器。HandyEditor编辑器十分轻量,并且使用便利,可定制,多语言支持,注重用户体验。HandyEditor编辑器的特点:轻量HandyEditor编辑器1.X版所有文件的压缩包只有90KB左右,是目前最为轻量的HTML编辑器之一。这保证了编辑器加载速度快,流量节省的特点,更适合于做

101 查看详情

101 查看详情

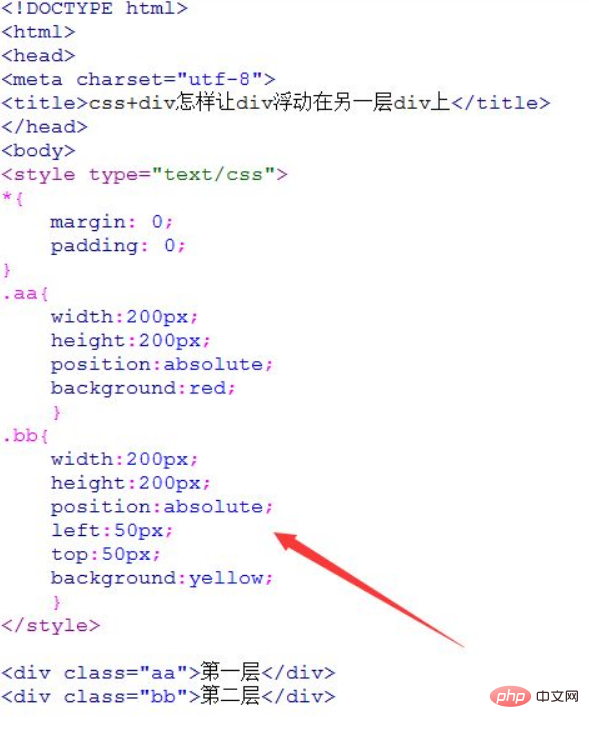

从端口映射的角度来看,SystemVerilog支持Verilog传统的一一映射方式,如下图代码第3行所示。同时也支持自动匹配,如代码第5行所示,.clk和.rst会自动与名为clk和rst的信号相连。而更为简洁的是代码第7行所示的.*连接方式,这表明所有端口将自动与其名字相同的信号相连。尽管这三种方式都是可综合的,但从代码风格角度而言,仍然建议采用第3行所示方式。在描述测试文件时,可以采用第7行所示方式。

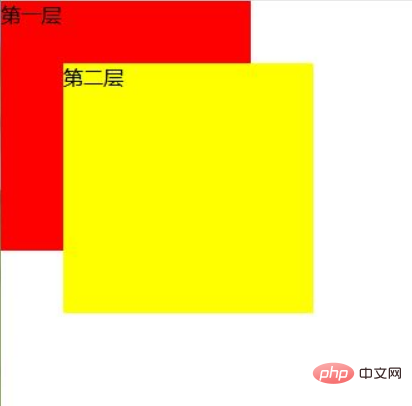

在Verilog中,给一个信号的所有位赋值为1,需要采用如下图所示的方式,而SystemVerilog可以直接采用下图代码第12行所示的方式。同时此方式还适用于赋值全0、全X和全Z。

在Verilog中,给一个信号的所有位赋值为1,需要采用如下图所示的方式,而SystemVerilog可以直接采用下图代码第12行所示的方式。同时此方式还适用于赋值全0、全X和全Z。

版权所有 @ FPGA技术驿站

版权所有 @ FPGA技术驿站

转载请私信 | 获得授权后方可转载

以上就是SystemVerilog不只是用于验证(2)的详细内容,更多请关注创想鸟其它相关文章!

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 chuangxiangniao@163.com 举报,一经查实,本站将立刻删除。

发布者:程序猿,转转请注明出处:https://www.chuangxiangniao.com/p/889349.html

微信扫一扫

微信扫一扫  支付宝扫一扫

支付宝扫一扫