大家好,又见面了,我是你们的朋友全栈君。

异步FIFO的空满判断也是通过地址位扩展来实现的,这一点与同步FIFO是相同的。然而,异步FIFO无法通过计数器来判断空满,且将地址转换为格雷码所带来的问题与同步FIFO的判断算法不同,这是异步FIFO的一个难点。关于格雷码的空满判断,请继续阅读下文。

异步FIFO的框架结构:

![关于异步FIFO的知识点–详细代码解释(很干)[通俗易懂]](https://cdn.chuangxiangniao.com/www/2025/11/175298556812995.jpg)

顶层代码:

module asyn_fifo(w_clk,rst_n,w_req,w_data,r_clk,r_req,r_data,w_full,r_empty); parameter DEPTH=256; //设置FIFO深度为256 parameter WIDTH_A=8; //根据FIFO深度进行地址编码 parameter WIDTH_D=16;//数据位宽为16 input w_clk; //写时钟 input rst_n; //复位信号 input w_req; // 写使能信号 input [WIDTH_D-1:0]w_data; // 写数据 input r_clk; // 读时钟 input r_req; // 读使能 output w_full; // 输出FIFO满信号 output r_empty; // 输出FIFO空信号 output [WIDTH_D-1:0]r_data; // 读数据 wire [WIDTH_A:0]w_addr; //写地址 wire [WIDTH_A:0]w_gaddr;//将地址转换成格雷码 wire [WIDTH_A:0]w_gaddr_syn;//转换成格雷码后的写地址同步到读时钟域去 wire [WIDTH_A:0]r_addr;// 读地址 wire [WIDTH_A:0]r_gaddr;// wire [WIDTH_A:0]r_gaddr_syn;// asyn_fifo_write_part write_control( //写控制 .rst_n(rst_n), .w_clk(w_clk), .w_req(w_req), .r_gaddr_syn(r_gaddr_syn), .w_full(w_full), .w_addr(w_addr), .w_gaddr(w_gaddr) ); asyn_fifo_syn syn_w_2_r( // 写地址同步到读时钟域 .rst_n(rst_n), .w_r_clk(r_clk), .w_r_gaddr(w_gaddr), .w_r_gaddr_syn(w_gaddr_syn) ); asyn_fifo_read_part read_control( // 读控制 .rst_n(rst_n), .r_clk(r_clk), .r_req(r_req), .w_gaddr_syn(w_gaddr_syn), .r_empty(r_empty), .r_addr(r_addr), .r_gaddr(r_gaddr) ); asyn_fifo_syn syn_r_2_w( // 读地址同步到 写时钟域 .rst_n(rst_n), .w_r_clk(w_clk), .w_r_gaddr(r_gaddr), .w_r_gaddr_syn(r_gaddr_syn) ); asyn_fifo_RAM_1 ram( // RAM存储 .rst_n(rst_n), .w_clk(w_clk), .r_clk(r_clk), .w_en(w_req & (!w_full)), .r_en(r_req & (!r_empty)), .w_data(w_data), .w_addr(w_addr[WIDTH_A-1:0]), .r_addr(r_addr[WIDTH_A-1:0]), .r_data(r_data) );endmodule

各部分代码:

(1)写控制模块

module asyn_fifo_write_part(rst_n,w_clk,w_req,w_gaddr,w_addr,w_full,r_gaddr_syn); parameter WIDTH_A=8; input rst_n; input w_clk; input w_req; //写使能 input [WIDTH_A:0]r_gaddr_syn; //同步后的读地址作为输入作用到写控制,进行写满判断 output [WIDTH_A:0]w_gaddr; //调用bin_to_gray模块,将二进制转换成格雷码 output [WIDTH_A:0]w_addr; output w_full; reg [WIDTH_A:0]w_addr; always @(posedge w_clk or negedge rst_n) begin if(!rst_n) w_addr <= 0; else if(w_req & (!w_full)) w_addr <= w_addr + 1'b1; end //假设地址位是3bit,所以FIFO深度为8,扩展一位后为4bit。先进行写操作,首先写入4个数据,此时的地址二进制表示为0100,格雷码表示为0110。然后数据被读取,//读地址二进制,为0100,格雷码也为0110,此时在读时钟域可判读为空。后连续写入8个数据,此时地址的二进制表示为1100,格雷码为1010,此时在写时钟域可判断////为写满。所以将二进制转换成格雷码带来的问题:通过格雷码进行空满判断就不能只考虑最高位的不同,需要进行最高位和次高位的取反,其余位保持即可判断。 assign w_full=({~w_gaddr[WIDTH_A],~w_gaddr[WIDTH_A-1],w_gaddr[WIDTH_A-2:0]}==r_gaddr_syn)?1'b1:1'b0; asyn_fifo_bin_to_gray bin_to_gray( .bin_c(w_addr), .gray_c(w_gaddr) );endmodule

(2)不同时钟域的两级同步模块:这一块没什么好解释的,就是打两拍同步,防止亚稳态传播

通义灵码

通义灵码

阿里云出品的一款基于通义大模型的智能编码辅助工具,提供代码智能生成、研发智能问答能力

31 查看详情

31 查看详情

module asyn_fifo_syn(rst_n,w_r_clk,w_r_gaddr,w_r_gaddr_syn); parameter WIDTH_D=8; input rst_n; input w_r_clk; input [WIDTH_D:0]w_r_gaddr; output [WIDTH_D:0]w_r_gaddr_syn; reg [WIDTH_D:0]w_r_gaddr_syn_1,w_r_gaddr_syn_2; always @(posedge w_r_clk or negedge rst_n) begin if(!rst_n) begin w_r_gaddr_syn_1 <= 0; w_r_gaddr_syn_2 <= 0; end else begin w_r_gaddr_syn_1 <= w_r_gaddr; w_r_gaddr_syn_2 <= w_r_gaddr_syn_1; end end assign w_r_gaddr_syn = w_r_gaddr_syn_2;endmodule

(3)读控制模块:空信号较易判断,地址相同即为空

module asyn_fifo_read_part(rst_n,r_clk,r_req,w_gaddr_syn,r_empty,r_addr,r_gaddr); parameter WIDTH_A=8; input rst_n; input r_clk; input r_req; input [WIDTH_A:0]w_gaddr_syn; output [WIDTH_A:0]r_addr; output [WIDTH_A:0]r_gaddr; output r_empty; reg [WIDTH_A:0]r_addr; always @(posedge r_clk or negedge rst_n) begin if(!rst_n) r_addr <= 0; else if(r_req & (!r_empty)) r_addr <= r_addr + 1'b1; end assign r_empty=(w_gaddr_syn==r_gaddr)?1'b1:1'b0; asyn_fifo_bin_to_gray bin_to_gray_2( .bin_c(r_addr), .gray_c(r_gaddr) );endmodule

(4)RAM模块

module asyn_fifo_RAM_1 #( parameter DEPTH = 256, parameter WIDTH_A = 8, //addr bit parameter WIDTH_D = 16 //data bit)( input r_clk, input w_clk, input rst_n, input [WIDTH_A-1:0] w_addr, input [WIDTH_D-1:0] w_data, input w_en, input [WIDTH_A-1:0] r_addr, input r_en, output reg[WIDTH_D-1:0] r_data); reg [15:0] mem[0:DEPTH-1]; integer i; always @( posedge w_clk ) begin if( !rst_n ) for(i=0;i<DEPTH;i=i+1) mem[i] <= 0; else if(w_en) mem[w_addr] <= w_data; end always @( posedge r_clk ) begin if( !rst_n ) r_data <= 0; else if(r_en) r_data <= mem[r_addr]; endendmodule

(5)二进制转换成格雷码bin_to_gray模块

module asyn_fifo_bin_to_gray(bin_c,gray_c); parameter WIDTH_D=8; input [WIDTH_D:0]bin_c; output [WIDTH_D:0]gray_c; wire h_b; assign h_b=bin_c[WIDTH_D]; reg [WIDTH_D-1:0]gray_c_d; integer i; always @(*) begin for(i=0;i<WIDTH_D;i=i+1) gray_c_d[i] = bin_c[i] ^ bin_c[i+1]; gray_c = {h_b,gray_c_d}; endendmodule

tb文件:

`timescale 1ns/1psmodule asyn_fifo_top_tb; reg rst_n; reg w_clk; reg r_clk; reg w_req; reg r_req; reg [15:0]w_data; wire [15:0]r_data; wire w_full; wire r_empty; always #2 w_clk=~w_clk; always #8 r_clk=~r_clk; asyn_fifo u1( .w_clk(w_clk), .rst_n(rst_n), .w_req(w_req), .w_data(w_data), .r_clk(r_clk), .r_req(r_req), .r_data(r_data), .w_full(w_full), .r_empty(r_empty) ); initial begin $vcdpluson(); end initial begin w_req=0; w_data=0; r_req=0; w_clk=0; r_clk=0; rst_n=0; #10; rst_n=1; #2; w_req=1; #10; r_req=1; forever begin @(posedge w_clk) if(!w_full) begin w_data = w_data + 1'b1; end end endendmodule

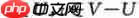

![关于异步FIFO的知识点–详细代码解释(很干)[通俗易懂]](https://cdn.chuangxiangniao.com/www/2025/11/175298556881220.jpg)

![关于异步FIFO的知识点–详细代码解释(很干)[通俗易懂]](https://cdn.chuangxiangniao.com/www/2025/11/175298556826542.jpg)

在仿真中验证了逻辑的正确性。

发布者:全栈程序员栈长,转载请注明出处:https://www.php.cn/link/2f75f02d15ae1f6ed96adc5761351562原文链接:https://www.php.cn/link/c8377ad2a50fb65de28b11cfc628d75c

以上就是关于异步FIFO的知识点–详细代码解释(很干)[通俗易懂]的详细内容,更多请关注创想鸟其它相关文章!

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 chuangxiangniao@163.com 举报,一经查实,本站将立刻删除。

发布者:程序猿,转转请注明出处:https://www.chuangxiangniao.com/p/456780.html

微信扫一扫

微信扫一扫  支付宝扫一扫

支付宝扫一扫

![[译]C++17, 语言核心层变化的更多细节](https://cdn.chuangxiangniao.com/www/2025/10/175306681248283.jpg?imageMogr2/crop/480x300/gravity/center)

![从零开始学习UCOSII操作系统15–总结篇[通俗易懂]](https://cdn.chuangxiangniao.com/www/2025/11/175245819985918.jpg)

![从零开始学习UCOSII操作系统15–总结篇[通俗易懂]](https://cdn.chuangxiangniao.com/www/2025/11/175245820229407.jpg)

![从零开始学习UCOSII操作系统15–总结篇[通俗易懂]](https://cdn.chuangxiangniao.com/www/2025/11/175680338913523-194.png)